Chris Jenkins

Chris Jenkins's Articles

Key iOS Chip Architect Gerard Williams III Departs Apple

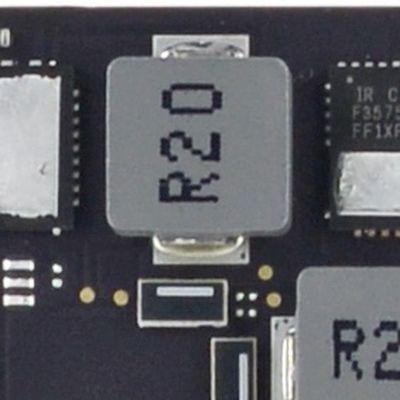

Throttling in New i9 MacBook Pros Appears to be Due to Power Delivery Chip

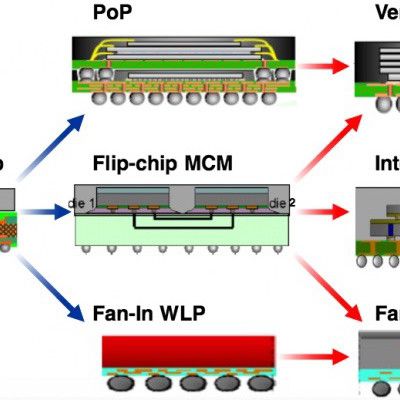

Patent Applications Reveal Apple's Research Into 3D Chip Packaging

Apple's Workforce Growth in Oregon Could Point to Desktop-Class CPU Ambitions

Intel Foundries Continue to Face Issues and Another Spectre-Like Vulnerability Disclosure May Be Looming

TSMC Details Technology Roadmap With Multiple Offerings to Benefit Future Apple Devices

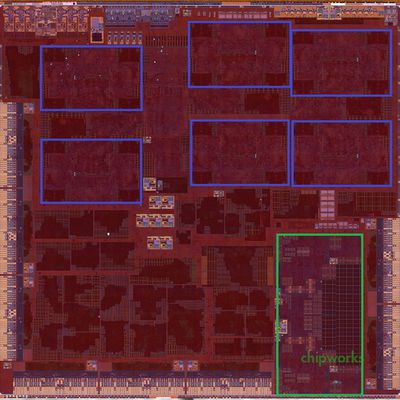

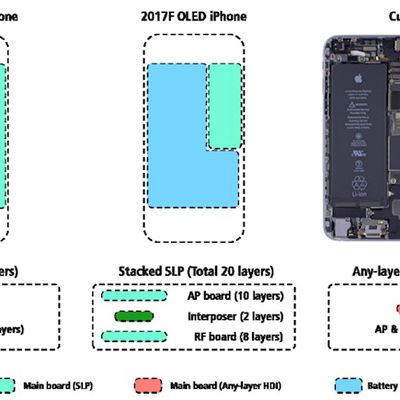

Prime Real Estate: The Fight for Space in the iPhone X

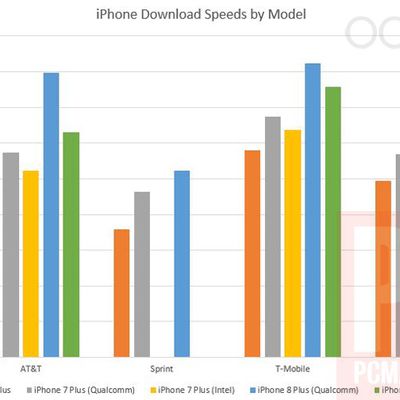

iPhone 8 Shows Modest Improvements in Cellular Network Bandwidth Tests

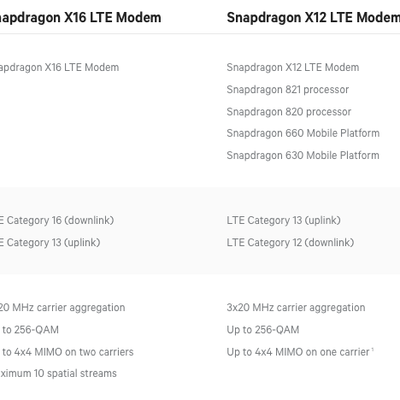

iPhone 8 Teardowns Reveal Advanced Modems Likely Selected for Power Improvements

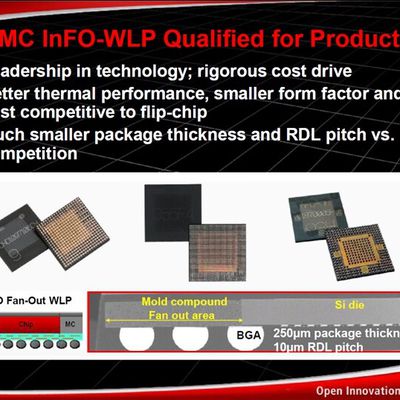

Apple's Chip Partner TSMC Shares Details on 7nm Node and Advanced InFO Package Process for 2018

A11 Chip's 6-Core Architecture Highlights Apple's Continuing Push Into Heterogeneous Computing

A Closer Look at Apple's CPU Improvements for iPhone 7 and Apple Watch

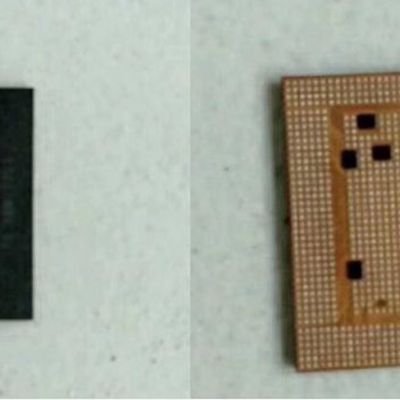

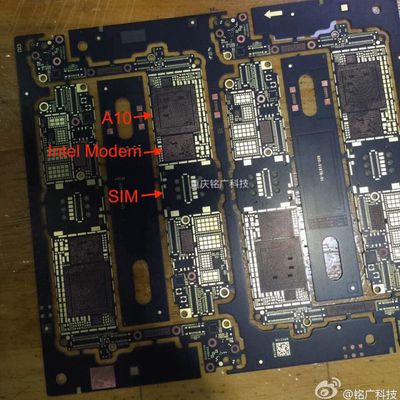

Leaked iPhone 7 Logic Boards Suggest Intel Modem, Other Component Tweaks

How TSMC Won Back Exclusivity With Apple for the A10 Chip in iPhone 7

New Semiconductor Processes Offer Power Efficiency Opportunities for Apple Watch

Samsung Said to Supply Apple with NAND Flash Memory in 2017 After Five-Year Hiatus

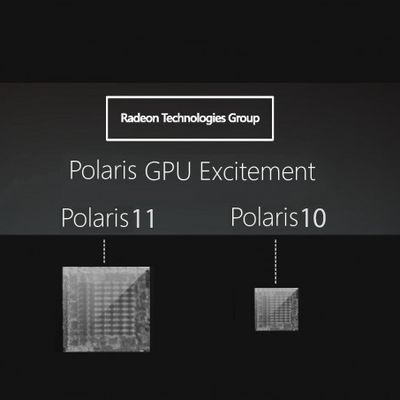

AMD's New 400-Series 'Polaris' Graphics Chips Headed for 2016 Macs

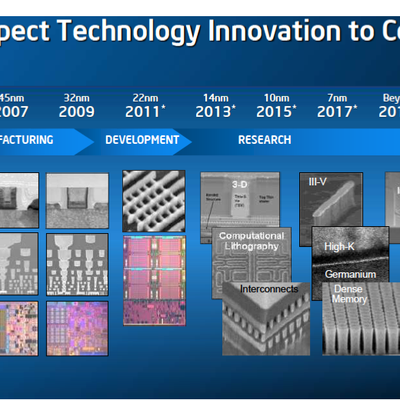

Mac Update Cycle Faces Uncertainty as Intel Abandons Tick-Tock Strategy

Apple's Mac Lineups to See Significant Graphics Upgrades as New GPU Launches Loom