Apple Silicon M1 Emulating x86 is Still Faster Than Every Other Mac in Single Core Benchmark

The first native benchmarks of Apple's M1 chip appeared on the Geekbench site last week showing impressive native performance. Today, new benchmarks have begun showing up for the M1 chip emulating x86 under Rosetta 2.

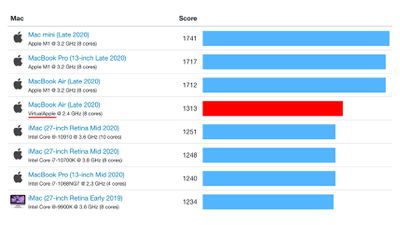

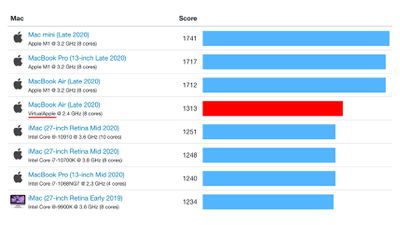

Single Core Mac benchmarks

The new Rosetta 2 Geekbench results uploaded show that the M1 chip running on a MacBook Air with 8GB of RAM has single-core and multi-core scores of 1,313 and 5,888 respectively. Since this version of Geekbench is running through Apple's translation layer Rosetta 2, an impact on performance is to be expected. Rosetta 2 running x86 code appears to be achieving 78%-79% of the performance of native Apple Silicon code.

Despite the impact on performance, the single-core Rosetta 2 score results still outperforms any other Intel Mac, including the 2020 27-inch iMac with Intel Core i9-10910 @ 3.6GHz.

Initial benchmarks for the MacBook Air running M1 natively featured a single-core score of 1,687 and multi-core score of 7,433. Additional benchmarks with M1 have since surfaced and are available on Geekbench.

Meanwhile, a full chart of Geekbench results is available that will let you compare these scores to any other Mac.

Popular Stories

Apple has announced it will be holding a special event on Tuesday, May 7 at 7 a.m. Pacific Time (10 a.m. Eastern Time), with a live stream to be available on Apple.com and on YouTube as usual. The event invitation has a tagline of "Let Loose" and shows an artistic render of an Apple Pencil, suggesting that iPads will be a focus of the event. Subscribe to the MacRumors YouTube channel for more ...

Apple today released several open source large language models (LLMs) that are designed to run on-device rather than through cloud servers. Called OpenELM (Open-source Efficient Language Models), the LLMs are available on the Hugging Face Hub, a community for sharing AI code. As outlined in a white paper [PDF], there are eight total OpenELM models, four of which were pre-trained using the...

Apple has dropped the number of Vision Pro units that it plans to ship in 2024, going from an expected 700 to 800k units to just 400k to 450k units, according to Apple analyst Ming-Chi Kuo. Orders have been scaled back before the Vision Pro has launched in markets outside of the United States, which Kuo says is a sign that demand in the U.S. has "fallen sharply beyond expectations." As a...

Apple is finally planning a Calculator app for the iPad, over 14 years after launching the device, according to a source familiar with the matter. iPadOS 18 will include a built-in Calculator app for all iPad models that are compatible with the software update, which is expected to be unveiled during the opening keynote of Apple's annual developers conference WWDC on June 10. AppleInsider...

The upcoming iOS 17.5 update for the iPhone includes only a few new user-facing features, but hidden code changes reveal some additional possibilities. Below, we have recapped everything new in the iOS 17.5 and iPadOS 17.5 beta so far. Web Distribution Starting with the second beta of iOS 17.5, eligible developers are able to distribute their iOS apps to iPhone users located in the EU...

Top Rated Comments

On die memory: there is no on die memory. It’s in the package, but not on the die. This is easy to see from the actual die photographs that have appeared on Ars (I addressed this claim in another thread and posted the picture). There are a number of LPDDR4X channels with off-chip drivers, so you can even see how the die connects to off-die RAM. Here’s the photo: https://images.anandtech.com/doci/16226/M1.png

”width”: what width are you referring to? There is nothing unusual about the execution width. It’s, in fact, identical to that used in, say Athlon-64 and Opteron. (I know, because I owned the integer execution unit for the first of those designs)

Dedicated units: most chips are now designed as SoC with on-chip encryption units, etc. AMD transitioned to that design methodology with Bulldozer. I know, because I left AMD right around when that started happening.

The CPU portion of the chip is very similar to every other CPU I ever designed. The SoC methodology is now a very common methodology.

What’s different here is competence, not some radical difference between M1 and x86 chips.

It’s got way more performance than any of the competition, and two or three times the battery life.

Aren’t those good reasons?

Oh, I know. They’ll fall back to “but it doesn’t virtualize x86.”

Anyway, that’s actually more of a Rosetta-speed hit than I expected, but we’ll see when we get real world data.